# 5 BIT PROGRAMMABLE STEP DOWN CONTROLLER WITH SYNCHRONOUS RECTIFICATION

- OPERATING SUPPLY IC VOLTAGE FROM 5V TO 12V BUSES

- UP TO 1.3A GATE CURRENT CAPABILITY

- TTL-COMPATIBLE 5 BIT PROGRAMMABLE OUTPUT COMPLIANT WITH VRM 9.0 : 1.100V TO 1.850V WITH 0.025V BINARY STEPS

- VOLTAGE MODE PWM CONTROL

- EXCELLENT OUTPUT ACCURACY: ±1% OVER LINE AND TEMPERATURE VARIATIONS

- VERY FAST LOAD TRANSIENT RESPONSE: FROM 0% TO 100% DUTY CYCLE

- POWER GOOD OUTPUT VOLTAGE

- OVERVOLTAGE PROTECTION AND MONITOR

- OVERCURRENT PROTECTION REALIZED USING THE UPPER MOSFET'S RdsON

- 200KHz INTERNAL OSCILLATOR

- OSCILLATOR EXTERNALLY ADJUSTABLE FROM 50KHz TO 1MHz

- SOFT START AND INHIBIT FUNCTIONS

#### APPLICATIONS

- POWER SUPPLY FOR AD (INCED MICROPROCESSOR CORE)

- DISTRIBUTED POWER SUPPLY

- HIGH POWER D° DC REGULATOPS

#### DESCRIPTION

The device is a power supply controller specifically designed to provide a high performance EC/DC conversion for high current microprocessors. A precise 5-bit digital to analog converter (DAC) allows adjusting the output volvage from 1.30V to 2.05 / with 50mV binary steps and from 2.10V to 3.50 / with 100mV binary steps.

The high precision in anal reference assures the selected output volvege to be within ±1%. The high peak current gate drive affords to have fast switching to the external power mos providing low switching losses.

The device assures a fast protection against load overcurrent and load overvoltage. An external SCR is inggered to crowbar the input supply in case of hard over-voltage. An internal crowbar is also provided turning on the low side mosfet as long as the overvoltage is detected. In case of over-current detection, the soft start capacitor is discharged and the system works in HICCUP mode.

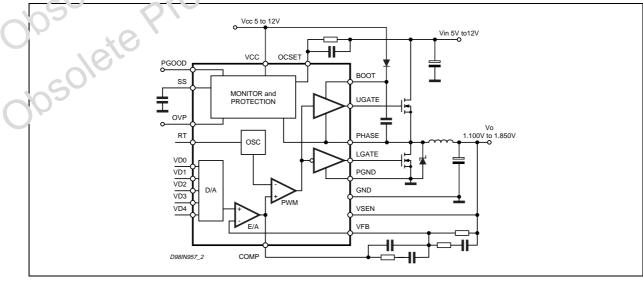

#### BLOCK D'AGRAM

November 2001

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                 | Parameter                       | Value           | Unit |

|----------------------------------------|---------------------------------|-----------------|------|

| V <sub>CC</sub>                        | V <sub>CC</sub> to GND, PGND    | 15              | V    |

| V <sub>BOOT</sub> -V <sub>PHASE</sub>  | Boot Voltage                    | 15              | V    |

| V <sub>HGATE</sub> -V <sub>PHASE</sub> |                                 | 15              | V    |

|                                        | OCSET, LGATE, PHASE             | -0.3 to Vcc+0.3 | V    |

|                                        | RT, SS, FB, PGOOD, VSEN, VID0-4 | 7               | V    |

|                                        | OVP, COMP                       | 6.5             | V    |

| HERMAL DAT                             | A                               | Auct            | 51   |

| Symbol                                 | Parameter                       | Value           | Unit |

#### THERMAL DATA

| Symbol                | Parameter                              |          | Value      | Unit |

|-----------------------|----------------------------------------|----------|------------|------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction to Ambient |          | 110        | °C/W |

| Tj                    | Maximum junction temperature           |          | 150        | °C   |

| T <sub>stg</sub>      | Storage temperature range              | <u> </u> | -40 to 150 | °C   |

| TJ                    | Junction temperature range             | 003      | 0 to 125   | °C   |

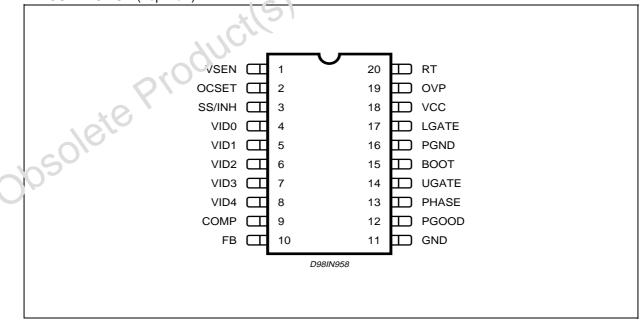

# **PIN CONNECTION** (Top view)

# **PIN FUNCTION**

| Pin<br>Num. | Name     | Description                                                                                                                                                                                                                                                                                 |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | VSEN     | Connected to the output voltage is able to manage over-voltage conditions and the PGOOD signal.                                                                                                                                                                                             |

| 2           | OCSET    | A resistor connected from this pin and the upper Mos Drain sets the current limit protection.<br>The internal $200\mu$ A current generator sinks a current from the drain through the external resisto<br>The Over-Current threshold is due to the following equation:                      |

|             |          | $I_{P} = \frac{I_{OCSET} \cdot R_{OCSET}}{R_{DSon}}$                                                                                                                                                                                                                                        |

| 3           | SS/INH   | The soft start time is programmed connecting an external capacitor from this pin and GND. Th internal current generator forces through the capacitor $10\mu$ A. This pin can be used to disable the device forcing a voltage lower than 0.4V                                                |

| 4 - 8       | VID0 - 4 | Voltage Identification Code pins. These input are internally pulled-up and TTL compatible. The are used to program the output voltage as specified in Table 1 and to set the overvoltage and power good thresholds.<br>Connect to GND to program a '0' while leave floating to program a '1 |

| 9           | COMP     | This pin is connected to the error amplifier output and is used 1° compensate the voltage contro<br>feedback loop.                                                                                                                                                                          |

| 10          | FB       | This pin is connected to the error amplifier inverting inrun and is used to compensate the voltag control feedback loop.                                                                                                                                                                    |

| 11          | GND      | All the internal references are referred to the pin. Connect it to the PCB signal ground.                                                                                                                                                                                                   |

| 12          | PGOOD    | This pin is an open collector output and is pulled low if the output voltage is not within the above specified thresholds.<br>If not used may be left floating.                                                                                                                             |

| 13          | PHASE    | This pin is connected to the source of the upper mosfet and provides the return path for the hig side driver. This pin mentions the drop across the upper mosfet for the current limit                                                                                                      |

| 14          | UGATE    | High side gate criver output.                                                                                                                                                                                                                                                               |

| 15          | BOOT     | Bootst.ap capacitor pin. Through this pin is supplied the high side driver and the upper mosfet.<br>Connect through a capacitor to the PHASE pin and through a diode to Vcc (cathode vs. boot).                                                                                             |

| 16          | PGND     | Power ground pin. This pin has to be connected closely to the low side mosfet source in order t reduce the noise injection into the device                                                                                                                                                  |

| 17          | CATE     | This pin is the lower mosfet gate driver output                                                                                                                                                                                                                                             |

| 61          | VCC      | Device supply voltage. The operative nominal supply voltage ranges from 5 to 12V. DO NOT CONNECT V <sub>IN</sub> TO A VOLTAGE GREATER THAN V <sub>CC</sub> .                                                                                                                                |

| 19          | OVP      | Over voltage protection. If the output voltage reaches the 17% above the programmed voltage this pin is driven high and can be used to drive an external SCR that crowbar the supply voltag If not used, it may be left floating.                                                           |

| 20          | RT       | Oscillator switching frequency pin. Connecting an external resistor from this pin to GND, the external frequency is increased according to the equation:                                                                                                                                    |

|             |          | $f_{S} = 200 \text{ kHz} + \frac{4.94 \cdot 10^{6}}{R_{T}(k\Omega)}$                                                                                                                                                                                                                        |

|             |          | Connecting a resistor from this pin to Vcc (12V), the switching frequency is reduced according the equation:                                                                                                                                                                                |

|             |          | $f_{S} = 200 \text{kHz} - \frac{4.306 \cdot 10^7}{\text{R}_{T}(\text{k}\Omega)}$                                                                                                                                                                                                            |

|             |          | If the pin is not connected, the switching frequency is 200KHz.<br>The voltage at this pin is fixed at 1.23V (typ). Forcing a 50µA current into this pin, the built in oscillator stops to switch.                                                                                          |

\_\_\_\_\_

| Symbol              | Parameter                                       | Test Condition                                                            | Min. | Тур. | Max. | Unit  |

|---------------------|-------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-------|

| V <sub>CC</sub> SUP | PLY CURRENT                                     |                                                                           |      |      |      |       |

| lcc                 | Vcc Supply current                              | UGATE and LGATE open                                                      |      | 5    |      | mA    |

| POWER-0             | NC                                              |                                                                           |      |      |      |       |

|                     | Turn-On Vcc threshold                           | VOCSET=4.5V                                                               | 1    |      | 4.6  | V     |

|                     | Turn-Off Vcc threshold                          | VOCSET=4.5V                                                               | 3.6  |      |      | V     |

|                     | Rising VOCSET threshold                         |                                                                           |      | 1.24 |      | V     |

| I <sub>SS</sub>     | Soft start Current                              |                                                                           |      | 10   |      | μA    |

| OSCILLA             | TOR                                             |                                                                           |      |      |      |       |

|                     | Free running frequency                          | R <sub>T</sub> = OPEN                                                     | 180  | 200  | 22)  | i kHz |

|                     | Total Variation                                 | 6 KΩ < RT to GND < 200 KΩ                                                 | -15  |      | 15   | %     |

| ΔVosc               | Ramp amplitude                                  | R <sub>T</sub> = OPEN                                                     |      | 1.9  |      | Vp-p  |

|                     |                                                 |                                                                           |      | 0    |      |       |

|                     | DACOUT Voltage                                  | VID0, VID1, VID2, VID3, VID4                                              | TO C |      | 1    | %     |

|                     | Accuracy                                        | see Table1; Tamb = 0 to 70°C                                              |      |      |      |       |

|                     | VID Pull-Up voltage                             | A CAR                                                                     | 1    | 4    |      | V     |

| ERROR A             | MPLIFIER                                        |                                                                           | 1    |      |      |       |

|                     | DC Gain                                         | S                                                                         |      | 88   |      | dB    |

| GBWP                | Gain-Bandwidth Product                          | 00                                                                        |      | 10   |      | MHz   |

| SR                  | Slew-Rate                                       | COMP=1upF                                                                 |      | 10   |      | V/µS  |

| GATE DR             | IVERS                                           |                                                                           | 1    |      |      |       |

| IUGATE              | High Side Source<br>Current                     | V'300T - VPHASE=12V,<br>VUGATE - VPHASE= 6V                               | 1    | 1.3  |      | A     |

| R <sub>UGATE</sub>  | High Side Sink<br>Resistance                    | V <sub>BOOT</sub> -V <sub>PHASE</sub> =12V,<br>I <sub>UGATE</sub> = 300mA |      | 2    | 4    | Ω     |

| I <sub>LGATE</sub>  | Low Side Source                                 | Vcc=12V, V <sub>LGATE</sub> = 6V                                          | 0.9  | 1.1  |      | A     |

| Rlgate              | Low Star Sink<br>Resistance                     | Vcc=12V, I <sub>LGATE</sub> = 300mA                                       |      | 1.5  | 3    | Ω     |

| -0                  | Output Driver Dead Time                         | PHASE connected to GND                                                    |      | 120  |      | ns    |

| FRUTECT             | TIONS                                           |                                                                           |      |      |      |       |

| <b>-</b>            | Over Voltage Trip<br>(V <sub>SEN</sub> /DACOUT) | V <sub>SEN</sub> Rising                                                   |      | 117  | 120  | %     |

| IOCSET              | OCSET Current Source                            | V <sub>OCSET</sub> = 4.5V                                                 | 170  | 200  | 230  | μA    |

| I <sub>OVP</sub>    | OVP Sourcing Current                            | V <sub>SEN</sub> > OVP Trip, V <sub>OVP</sub> =0V                         | 60   |      |      | mA    |

| POWER               | GOOD                                            |                                                                           | 1    | l    | 1    | I     |

|                     | Upper Threshold<br>(V <sub>SEN</sub> /DACOUT)   | V <sub>SEN</sub> Rising                                                   | 110  | 112  | 114  | %     |

|                     | Lower Threshold<br>(V <sub>SEN</sub> /DACOUT)   | V <sub>SEN</sub> Falling                                                  | 86   | 88   | 90   | %     |

|                     | Hysteresis<br>(V <sub>SEN</sub> /DACOUT)        | Upper and Lower threshold                                                 |      | 2    |      | %     |

| V <sub>PGOOD</sub>  | PGOOD Voltage Low                               | I <sub>PGOOD</sub> = -5mA                                                 | -    | 0.5  |      | V     |

57

4/17

| VID4 | VID3 | VID2 | VID1 | VID0 | Output<br>Voltage (V) | VID4 | VID3 | VID2 | VID1 | VID0 | Output Voltage<br>(V) |

|------|------|------|------|------|-----------------------|------|------|------|------|------|-----------------------|

| 1    | 1    | 1    | 1    | 1    | Output OFF            | 0    | 1    | 1    | 1    | 1    | 1.475                 |

| 1    | 1    | 1    | 1    | 0    | 1.100                 | 0    | 1    | 1    | 1    | 0    | 1.500                 |

| 1    | 1    | 1    | 0    | 1    | 1.125                 | 0    | 1    | 1    | 0    | 1    | 1.525                 |

| 1    | 1    | 1    | 0    | 0    | 1.150                 | 0    | 1    | 1    | 0    | 0    | 1.550                 |

| 1    | 1    | 0    | 1    | 1    | 1.175                 | 0    | 1    | 0    | 1    | 1    | 1.575                 |

| 1    | 1    | 0    | 1    | 0    | 1.200                 | 0    | 1    | 0    | 1    | 0    | 1.600                 |

| 1    | 1    | 0    | 0    | 1    | 1.225                 | 0    | 1    | 0    | 0    | 1    | 1.625                 |

| 1    | 1    | 0    | 0    | 0    | 1.250                 | 0    | 1    | 0    | 0    | 0    | 1.650                 |

| 1    | 0    | 1    | 1    | 1    | 1.275                 | 0    | 0    | 1    | 1    | 1    | 1.673                 |

| 1    | 0    | 1    | 1    | 0    | 1.300                 | 0    | 0    | 1    | 1    | 0    | 1.700                 |

| 1    | 0    | 1    | 0    | 1    | 1.325                 | 0    | 0    | 1    | 0    | 1    | 1.725                 |

| 1    | 0    | 1    | 0    | 0    | 1.350                 | 0    | 0    | 1    | 0    | 0    | 1.750                 |

| 1    | 0    | 0    | 1    | 1    | 1.375                 | 0    | 0    | 0    | 1    | 0    | 1.775                 |

| 1    | 0    | 0    | 1    | 0    | 1.400                 | 0    | 0    | 0    |      | 0    | 1.800                 |

| 1    | 0    | 0    | 0    | 1    | 1.425                 | 0    | 0    | 0    | 0    | 1    | 1.825                 |

| 1    | 0    | 0    | 0    | 0    | 1.450                 | 0    | 0    | 6    | 0    | 0    | 1.850                 |

#### Table 1. VID Settings

#### **Device Description**

The device is an integrated circuit realized in BCD technology is provides complete control logic and protections for a high performance step-down DC-DC converter optimized for microprocessor power supply. It is designed to drive N-Channel Mosfets in a synchronous-rectified buck topology. The device works properly with Vcc ranging from 5V to 12V and regulates the output voltage starting from a 1.26V power stage supply voltage (Vin). The output voltage of the converter can be precisely regulated, programming the VID pins, from 1.100V to 1.850V with 25mV binary steps, with a maximum colerance of  $\pm 1\%$  over temperature and line voltage variations. The device provides voltage-mode control with fast transient response. It includes a 200kHz free-running oscillator that is adjustable from 50kHz (o 1).

The error amplifier features a 15iMHz gain-bandwidth product and  $10V/\mu s$  slew rate which permits high converter bandwidth for fast transient performance. The resulting PWM duty cycle ranges from 0% to 100%. The device protects against over-current conditions entering in HICCUP mode. The device monitors the current by using the  $r_{DS(ON)}$  of the upper MOSFET which eliminates the need for a current sensing resistor.

The device is available in SO20 package

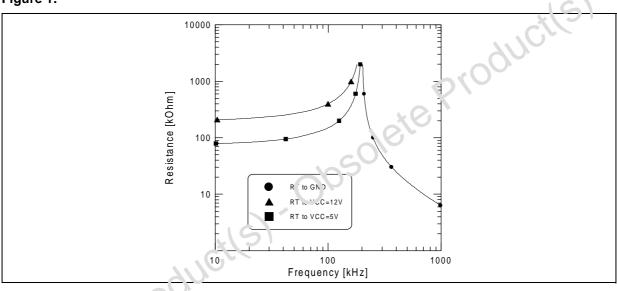

#### **Os** cinator

The switching frequency is internally fixed to 200kHz. The internal oscillator generates the triangular waveform for the PWM charging and discharging with a constant current an internal capacitor. The current delivered to the oscillator is typically  $50\mu$ A (Fsw=200KHz) and may be varied using an external resistor (R<sub>T</sub>) connected between RT pin and GND or VCC. Since the RT pin is maintained at fixed voltage (typ. 1.235V), the frequency is varied proportionally to the current sunk (forced) from (into) the pin.

In particular connecting it to GND the frequency is increased (current is sunk from the pin), according to the following relationship:

$$f_{S} = 200 \text{kHz} + \frac{4.94 \cdot 10^{\circ}}{\text{R}_{T}(\text{k}\Omega)}$$

Connecting RT to VCC=12V or to VCC=5V the frequency is reduced (current is forced into the pin), according to the following relationships:

$$f_{S} = 200 \text{ kHz} + \frac{4.306 \cdot 10^{7}}{R_{T}(k\Omega)} \qquad V_{CC} = 12 \text{ V}$$

$$f_{S} = 200 \text{ kHz} + \frac{15 \cdot 10^{7}}{R_{T}(k\Omega)} \qquad V_{CC} = 5 \text{ V}$$

Switching frequency variations vs. RT are reported in Fig.1.

Note that forcing a  $50\mu A$  current into this pin, the device stops switching because no current is delivered to the oscillator.

#### Digital to Analog Converter

The built-in digitar to analog converter allows the adjustment of the output voltage from 1.30V to 2.05V with 50mV binary steps and from 2.10V to 3.50V with 100mV binary steps as shown in the previous table 1. The internal reference is trimmed to ensure the precision of 1%.

The internal reference voltage for the regulation is programmed by the voltage identification (VID) pins. These are in L compatible inputs of an internal DAC that is realized by means of a series of resistors providing a partition of the internal voltage reference. The VID code drives a multiplexer that selects a voltage on a precise point of the divider. The DAC output is delivered to an amplifier obtaining the V<sub>PROG</sub> voltage reference (i.e. the set-point of the error amplifier). Internal pull-ups are provided (realized with a 5µA current generator); in this way, to program a logic "1" it is enough to leave the pin floating, while to program a logic "0" it is enough to short the pin to GND.

The voltage identification (VID) pin configuration also sets the power-good thresholds (PGOOD) and the overvoltage protection (OVP) thresholds.

The VID code "11111" disable the device (as a short on the SS pin) and no output voltage is regulated.

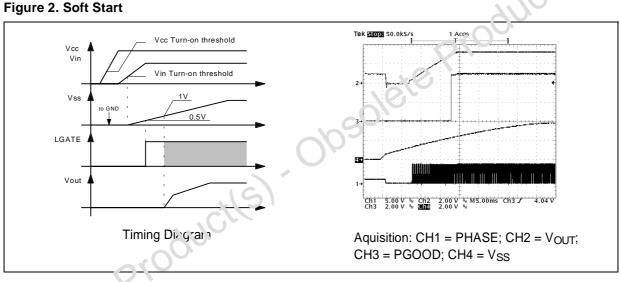

#### Soft Start and Inhibit

At start-up a ramp is generated charging the external capacitor  $C_{SS}$  by means of a 10µA constant current, as shown in figure 1.

When the voltage across the soft start capacitor (VSS) reaches 0.5V the lower power MOS is turned on to dis-

charge the output capacitor. As VSS reaches 1V (i.e. the oscillator triangular wave inferior limit) also the upper MOS begins to switch and the output voltage starts to increase.

The V<sub>SS</sub> growing voltage initially clamps the output of the error amplifier, and consequently  $V_{OUT}$  linearly increases, as shown in figure 2. In this phase the system works in open loop. When VSS is equal to VCOMP the clamp on the output of the error amplifier is released. In any case another clamp on the input of the error amplifier remains active, allowing to V<sub>OUT</sub> to grow with a lower slope (i.e. the slope of the V<sub>SS</sub> voltage, see figure 2). In this second phase the system works in closed loop with a growing reference. As the output voltage reaches the desired value VPROG, also the clamp on the error amplifier input is removed, and the soft start finishes. Vss increases until a maximum value of about 4V.

The Soft-Start will not take place, and the relative pin is internally shorted to GND, if both VCC and OCSET pins are not above their own turn-on thresholds. During normal operation, if any under-voltage is detected on one of the two supplies, the SS pin is internally shorted to GND and so the SS capacitor is rapidly discharged.

The device goes in INHIBIT state forcing SS pin below 0.4V. In this condition both external MOSFETS are kept off.

# Figure 2. Soft Start

#### Driver Section

The drive: car ability on the high and low side drivers allows using different types of power MOS (also multiple MOS to reduce the R<sub>DSON</sub>), maintaining fast switching transition.

The sw-side mos driver is supplied directly by Vcc while the high-side driver is supplied by the BOOT pin.

Adaptative dead time control is implemented to prevent cross-conduction and allow to use several kinds of mosfets. The upper mos turn-on is avoided if the lower gate is over about 200mV while the lower mos turn-on is avoided if the PHASE pin is over about 500mV. The upper mos is in any case turned-on after 200nS from the low side turn-off.

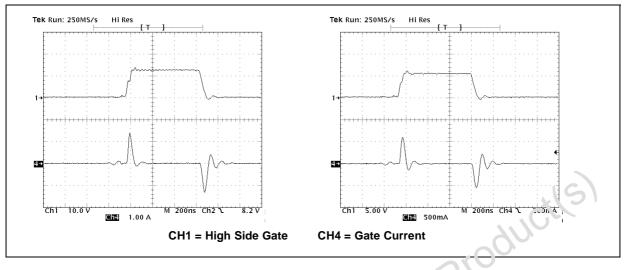

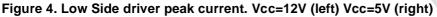

The peak current is shown for both the upper (fig. 3) and the lower (fig. 4) driver at 5V and 12V. A 4nF capacitive load has been used in these measurements.

For the lower driver, the source peak current is 1.1A @ Vcc=12V and 500mA @ Vcc=5V, and the sink peak current is 1.3A @ Vcc=12V and 500mA @ Vcc=5V.

Similarly, for the upper driver, the source peak current is 1.3A @ Vboot-Vphase=12V and 600mA @ Vboot-Vphase =5V, and the sink peak current is 1.3A @ Vboot-Vphase =12V and 550mA @ Vboot-Vphase = 5V.

Figure 3. High Side driver peak current. Vboot-Vphase=12V (left) Vboot-Vphase=5V (right)

#### Montoring and Protections

The output voltage is monitored by means of pin 1 (VSEN). If it is not within ±12% (typ.) of the programmed value, the powergood output is forced low.

The device provides overvoltage protection, when the output voltage reaches a value 17% (typ.) grater than the nominal one. If the output voltage exceeds this threshold, the OVP pin is forced high, triggering an external SCR to shuts the supply (VIN) down, and also the lower driver is turned on as long as the over-voltage is detected.

To perform the overcurrent protection the device compares the drop across the high side MOS, due to the RDSON, with the voltage across the external resistor (ROCS) connected between the OCSET pin and drain of the upper MOS. Thus the overcurrent threshold ( $I_P$ ) can be calculated with the following relationship:

$$I_{\rm P} = \frac{I_{\rm OCS} \cdot R_{\rm OCS}}{R_{\rm DSON}}$$

Where the typical value of  $I_{OCS}$  is 200µA. To calculate the ROCS value it must be considered the maximum R<sub>DSON</sub> (also the variation with temperature) and the minimum value of  $I_{OCS}$ . To avoid undesirable trigger of

overcurrent protection this relationship must be satisfied:

$$I_{P} \ge I_{OUTMAX} + \frac{\Delta I}{2} = I_{PEAK}$$

Where  $\Delta I$  is the inductance ripple current and  $I_{OUTMAX}$  is the maximum output current.

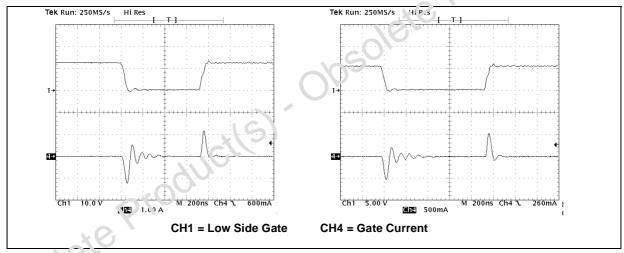

In case of output short circuit the soft start capacitor is discharged with constant current ( $10\mu$ A typ.) and when the SS pin reaches 0.5V the soft start phase is restarted. During the soft start the over-current protection is always active and if such kind of event occurs, the device turns off both mosfets, and the SS capacitor is discharged again (after reaching the upper threshold of about 4V). The system is now working in HICCUP mode, as shown in figure 5a. After removing the cause of the over-current, the device restart working normally without power supplies turn off and on.

#### Figure 5.

#### Inductor design

The inductance value is defined by a compromise between the transient response time, the efficiency, the cost and the size. The inductor has to be calculated to sustain the output and the input voltage variation to maintain the ripple current  $\Delta IL$  between 20% and 30% of the maximum output current. The inductance value can be calculated with this relationship:

$$L = \frac{V_{IN} - V_{OUT}}{f_{S} \cdot \Delta I_{L}} \cdot \frac{V_{OUT}}{V_{IN}}$$

Where  $f_{SW}$  is the switching frequency,  $V_{IN}$  is the input voltage and  $V_{OUT}$  is the output voltage. Figure 5b shows the ripple current vs. the output voltage for different values of the inductor, with  $V_{IN} = 5V$  and  $V_{IN} = 12V$ .

Increasing the value of the inductance reduces the ripple current but, at the same time, reduces the converter response time to a load transient. If the compensation network is well designed, the device is able to open or close the duty cycle up to 100% or down to 0%. The response time is now the time required by the inductor to change its current from initial to final value. Since the inductor has not finished its charging time, the output current is supplied by the output capacitors. Minimizing the response time can minimize the output capacitance required.

The response time to a load transient is different for the application or the removal of the load: if during the application of the load the inductor is charged by a voltage equal to the difference between the input and the output voltage, during the removal it is discharged only by the output voltage. The following expressions give approximate response time for  $\Delta I$  load transient in case of enough fast compensation network response:

$$t_{\text{application}} = \frac{L \cdot \Delta I}{V_{\text{IN}} - V_{\text{OUT}}} \qquad t_{\text{removal}} = \frac{L \cdot \Delta I}{V_{\text{OUT}}}$$

The worst condition depends on the input voltage available and the output voltage selected. Anyway the worst case is the response time after removal of the load with the minimum output voltage programmed and the maximum input voltage available.

#### **Output Capacitor**

Since the microprocessors require a current variation beyond 10A doing load transients, with a slope in the range of tenth A/ $\mu$ sec, the output capacitor is a basic component for the fast response of the power supply. In fact for first few microseconds they supply the current to the load. The controller recognizes immediately the load transient and sets the duty cycle at 100%, but the current slope is limited by the inductor value.

The output voltage has a first drop due to the current variation inside the capacitor (neglecting the effect of the ESL):

$$\Delta V_{OUT} = \Delta I_{OUT} \cdot ESR$$

A minimum capacitor value is required to sustain the current during the load transient without discharge it. The voltage drop due to the output capacitor discharge is given by the following equation:

**\ (**

$$\Delta V_{OUT} = \frac{\Delta I_{OUT}^2}{2 \cdot C_{OUT} \cdot (V_{IN'MIN} \cdot D_{MAX} - V_{OUT})}$$

Where D<sub>MAX</sub> is the maximum duty cycle value that is 100%. The lower is the ESR, the lower is the output drop during load transient and the lower is the output voltage static ripple.

#### **Input Capacitor**

The input capacitor has to sustain the ripple current produced during the on time of the upper MOS, so it must have a low ESR to minimize the losses. The rms value of this ripple is:

$$I_{\rm rms} = I_{\rm OUT} \sqrt{D \cdot (1 - D)}$$

Where D is the duty cycle. The equation reaches its maximum value with D=0.5. The losses in worst case are:

$$P = ESR \cdot I_{rms}^2$$

#### Compensation network design

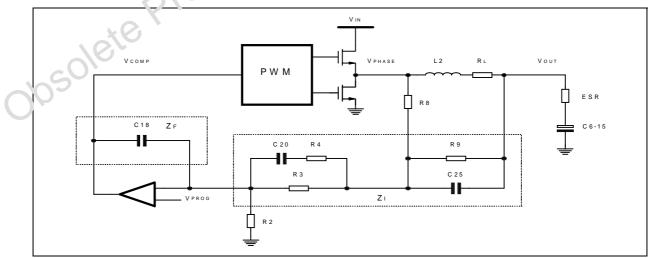

The control loop is a voltage mode (figure 7) that uses a droop function to satisfy the requirements for a VRM module, reducing the size and the cost of the output capacitor.

This method "recovers" part of the drop due to the output capacitor ESR in the load transient, introducing a dependence of the output voltage on the load current: at light load the output voltage will be higher than the nominal level, while at high load the output voltage will be lower than the nominal value.

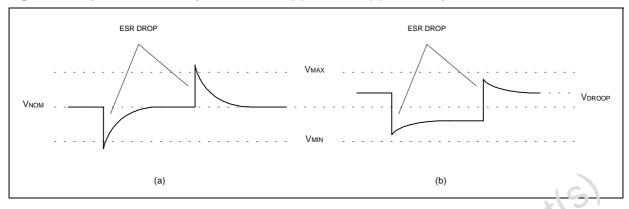

Figure 6. Output transient response without (a) and with (b) the droop function

As shown in figure 6, the ESR drop is present in any case, but using the droop function the total deviation of the output voltage is minimized. In practice the droop function introduces a static error (Vdroop in figure 6) proportional to the output current. Since a sense resistor is not present, the output DC current is measured by using the intrinsic resistance of the inductance (a few m $\Omega$ ). So the low-pass filtered in ductor voltage (that is the inductor current) is added to the feedback signal, implementing the droop function in a simple way. Referring to the schematic in figure 7, the static characteristic of the closed loop system is.

$$V_{OUT} = V_{PROG} + V_{PROG} \cdot \frac{R3 + R8 / R9}{R2} - \frac{R_L \cdot R8 / R9}{R8} \cdot I_{OUT}$$

Where  $V_{PROG}$  is the output voltage of the digital to analog converter (i.e. the set point) and R<sub>L</sub> is the inductance resistance. The second term of the equation allows a positive offset at zero load ( $\Delta V^+$ ); the third term introduces the droop effect ( $\Delta V_{DROOP}$ ). Note that the droop effect is equal the ESR drop if:

$$\frac{R_{L} \cdot R8 // R9}{R8} = ESR$$

Figure 7. Compensation network

<u>لرکا</u>

Considering the previous relationships R2, R3, R8 and R9 may be determined in order to obtain the desired droop effect as follow:

Choose a value for R2 in the range of hundreds of KΩ to obtain realistic values for the other components.

From the above equations, it results:

$$R8 = \frac{\Delta V^{+} \cdot R2}{V_{PROG}} \cdot \frac{R_{L} \cdot I_{MAX}}{\Delta V_{DROOP}};$$

$$R9 = R8 \cdot \frac{\Delta V_{DROOP}}{R_{L} \cdot I_{MAX}} \cdot \frac{1}{1 + \frac{\Delta V_{DROOP}}{R_{L} \cdot I_{MAX}}};$$

Where  $I_{MAX}$  is the maximum output current.

The component R3 must be chosen in order to obtain R3<<R8//R9 to permit these and successive simplifications.</p>

Therefore, with the droop function the output voltage decreases as the load current increases, so the DC output impedance is equal to a resistance R<sub>OUT</sub>. It is easy to verify that the output voltage deviation under load transient is minimum when the output impedance is constant with frequency.

To choose the other components of the compensation network, the transfer function of the voltage loop is considered. To simplify the analysis is supposed that R3 << Rd, where Rd = (R8//R9).

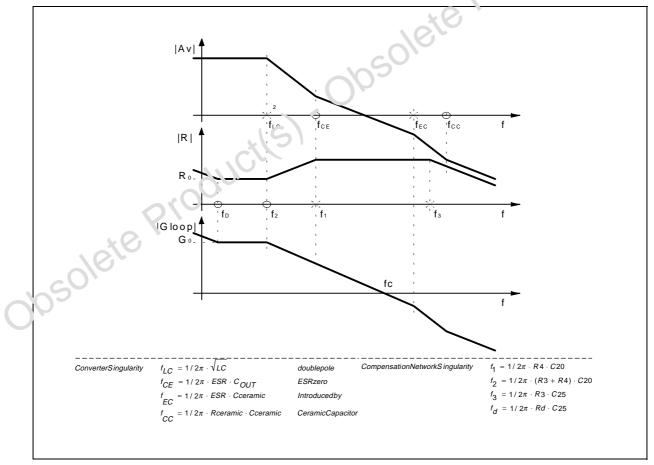

Figure 8. Compensation network definition

The transfer function may be evaluated neglecting the connection of R8 to PHASE because, as will see later, this connection is important only at low frequencies. So R4 is considered connected to VOUT. Under this assumption, the voltage loop has the following transfer function:

$$Gloop(s) = Av(s) \cdot R(s) = Av(s) \cdot \frac{Zf(s)}{Zi(s)} \text{ Where } Av(s) = \frac{Vin}{\Delta V_{osc}} \cdot \frac{Z_{C}(s)}{Z_{C}(s) + Z_{L}(s)}$$

Where  $Z_{C}(s)$  and  $Z_{L}(s)$  are the output capacitor and inductor impedance respectively. The expression of  $Z_{I}(s)$  may be simplified as follow:

$$Z_{I}(s) = \frac{Rd \cdot \frac{1}{s} \cdot C25}{Rd + \frac{1}{s} \cdot C25} + \frac{\left(R4 + \frac{1}{s} \cdot C20\right) \cdot R3}{\left(R4 + \frac{1}{s} \cdot C20\right) + R3} = \frac{Rd\left(1 + s \cdot (\tau_{1} + \tau_{d}) + s^{2} \cdot \frac{R3}{R_{d}} \cdot \tau_{1} \cdot \tau_{d}\right)}{(1 + s \cdot \tau_{2}) \cdot (1 + s \cdot \tau_{d})} = Rd\frac{\left(1 + s\frac{R3}{R_{d}} \cdot \tau_{d}\right) \cdot (1 + s \cdot \tau_{1})}{(1 + s \cdot \tau_{2}) \cdot (1 + s \cdot \tau_{d})}$$

$$\tau_{1} = R4 \times C20, \ \tau_{2} = (R4 + R3) \times C20 \ \text{and} \ \tau_{d} = Rd \times C25.$$

gulator transfer function became now:

Where:  $\tau_1 = R4 \times C20$ ,  $\tau_2 = (R4 + R3) \times C20$  and  $\tau_d = Rd \times C25$ . The regulator transfer function became now:

$$\mathsf{R}(s) \approx \frac{(1 + s \cdot \tau_2) \cdot (1 + s \cdot \tau_d)}{s \cdot \mathsf{C18} \cdot \mathsf{R}_d \cdot \left(1 + s \frac{\mathsf{R3}}{\mathsf{R}_d} \cdot \tau_d\right) (1 + s \cdot \tau_1)}$$

Figure 8 shows a method to select the regulator components (please note that the frequencies fEC and fCC corresponds to the singularities introduced by additional ceramic capacitors in parallel to the output main electrolytic capacitor).

• To obtain a flat frequency response of the output impedance, the droop time constant  $\tau_d$  has to be equal to the inductor time constant (see the note at the end of the section):

$$\tau_{d} - R_{d} \cdot C25 = \frac{L}{R_{L}} = \tau_{L} \qquad \Rightarrow C25 = \frac{L}{(R_{L} \cdot R_{d})}$$

■ To obtain a constant -20dB/dec Gloop(s) shape the singularity f<sub>1</sub> and f<sub>2</sub> are placed in proximity of f<sub>CE</sub> and  $f_{LC}$  respectively. This implies that:

$$\frac{f_2}{f_1} = \frac{f_{LC}}{f_{CE}} \implies R4 = R3 \cdot \left(\frac{f_{LC}}{f_{CE}} - 1\right)$$

$$f1 = f_{CE} \implies C20 = \frac{1}{2} \cdot \pi \cdot R4 \cdot f_{CE}$$

To obtain a Gloop bandwidth of f<sub>C</sub>, results:

$$G_0 \cdot f_{LC} = 1 \cdot f_C \quad \Rightarrow \quad G_0 = A_0 \cdot R_0 = \frac{VIN}{\Delta Vosc} \cdot \frac{C20 //C25}{C18} = \frac{f_C}{f_{LC}} \quad \Rightarrow \quad C18 = \frac{VIN}{\Delta Vosc} \cdot \frac{C20 \cdot C25}{C20 + C25} \cdot \frac{f_{LC}}{f_C}$$

#### Note.

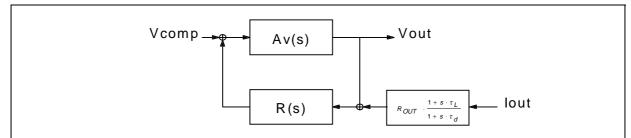

To understand the reason of the previous assumption, the scheme in figure 9 must be considered.

In this scheme, the inductor current has been substituted by the load current, because in the frequencies range of interest for the Droop function these current are substantially the same and it was supposed that the droop network don't represent a charge for the inductor.

#### Figure 9. Voltage regulation with droop function block scheme

It results:

$$Z_{OUT} = \frac{V_o}{I_{LOAD}} = R_d \cdot \frac{1 + s\tau_L}{1 + s\tau_d} \cdot \frac{G_{LOOP}}{1 + G_{LOOP}} = R_{OUT} \cdot \frac{1 + s\tau_L}{1 + s\tau_d}$$

ted range |Gloop|>>1.

the relationship considered will naturally follow.

Because in the interested range |Gloop|>>1.

To obtain a flat shape, the relationship considered will naturally follow.

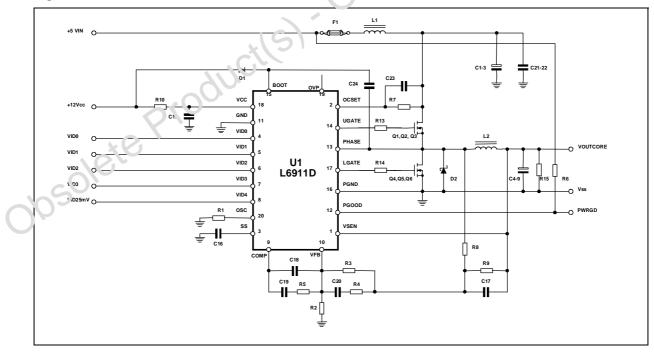

#### Application Idea: 1.100V to 1.850V / 25A

Figure 10 shows an application schematic for a 1.100V to 1.850V conversion with 25A of current capability. Since the device's high gate drive, more than one mosfet for both high cide and low side can be used: three STS11NF30L (30V, 9mW typ @ Vgs=10V) mosfet are suggested for high side while four of them are suggested as low side switch.

# Figure 10. Schematic Circuit

# Part List

| Resistor           |                            |                                |                                  |

|--------------------|----------------------------|--------------------------------|----------------------------------|

| R1                 | Not Mounted                |                                | SMD 0805                         |

| R2                 | 470                        | 1%                             | SMD 0805                         |

| R3                 | 1k                         |                                | SMD 0805                         |

| R4                 | 82                         |                                | SMD 0805                         |

| R5                 | Not Mounted                |                                | SMD 0805                         |

| R6                 | 1k                         |                                | SMD 0805                         |

| R7                 | 1k                         |                                | SMD 0805                         |

| R8                 | 13k                        |                                | SMD 0805                         |

| R9                 | 100k                       |                                | SMD 0805                         |

| R10                | Not Mounted                |                                | SMD 0805                         |

| R12                | 20k                        |                                | SMD 0805                         |

| R13, R14           | Short Circuit              |                                | SMD 1205                         |

| Capacitor          |                            |                                |                                  |

| C1-C3              | 680μF - 6.3V               | OSCON 6SP680M                  | Radial 10x10.5                   |

| C4-C9              | 820μF - 4V<br>680μF - 6.3V | OSCON 6SP680M<br>OSCON 4SP820M | Radial 10x10.5<br>Radial 10x10.5 |

| C16                | 100n                       | 18                             | SMD 0805                         |

| C17                | 100n                       | -010                           | SMD 0805                         |

| C18                | 2.2n                       | 103                            | SMD 0805                         |

| C19                | Not Mounted                |                                | SMD 0805                         |

| C20                | 100n                       |                                | SMD 0805                         |

| C23                | 1n                         |                                | SMD 0805                         |

| C24                | 100n                       |                                | SMD 0805                         |

| C25                | 47n                        |                                | SMD 0805                         |

| Magnetics          | 20                         |                                |                                  |

| L1                 | 1 5μΗ                      | T44-52 Core, 7T-18AWG          |                                  |

| L2                 | 1.8μΗ                      | T50-52B Core, 7T-16AWG         |                                  |

| Transistors        |                            |                                |                                  |

| Q1-Q5              | STS12NF30L                 | STMicroelectronics             | SO8                              |

| Diode <sub>3</sub> |                            |                                | 4                                |

| <u> </u>           | 1N4148                     | STMicroelectronics             | SOT23                            |

| 27                 | STPS3L25U                  | STMicroelectronics             | SMB                              |

| lcs                |                            |                                | 1                                |

| U1                 | L6911D                     | STMicroelectronics             | SO20                             |

| Fuse               | I                          | I                              | 1                                |

| F1                 | 251015A-15A                | Littlefuse                     | AXIAL                            |

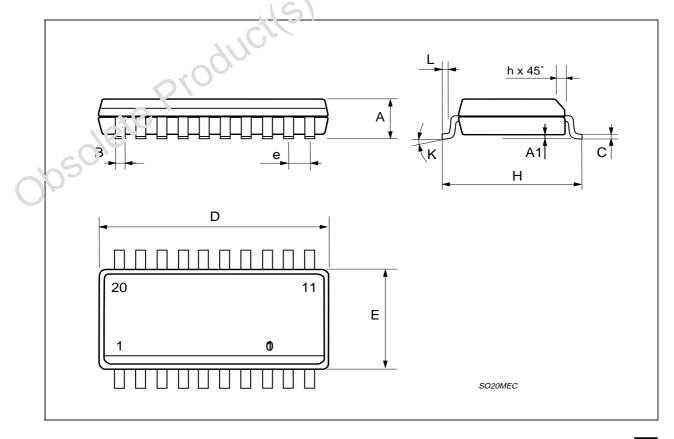

| DIM. | mm                 |      |       | inch  |       |       |  |  |

|------|--------------------|------|-------|-------|-------|-------|--|--|

|      | MIN.               | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |  |  |

| А    | 2.35               |      | 2.65  | 0.093 |       | 0.104 |  |  |

| A1   | 0.1                |      | 0.3   | 0.004 |       | 0.012 |  |  |

| В    | 0.33               |      | 0.51  | 0.013 |       | 0.020 |  |  |

| с    | 0.23               |      | 0.32  | 0.009 |       | 0.013 |  |  |

| D    | 12.6               |      | 13    | 0.496 |       | 0.512 |  |  |

| E    | 7.4                |      | 7.6   | 0.291 |       | 0.299 |  |  |

| е    |                    | 1.27 |       |       | 0.050 |       |  |  |

| н    | 10                 |      | 10.65 | 0.394 |       | 0.419 |  |  |

| h    | 0.25               |      | 0.75  | 0.010 |       | 0.030 |  |  |

| L    | 0.4                |      | 1.27  | 0.016 |       | 0.050 |  |  |

| к    | 0° (min.)8° (max.) |      |       |       |       |       |  |  |

# OUTLINE AND MECHANICAL DATA

16/17

Josolete Product(S) - Obsolete Product(S) Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

> The ST logo is a registered trademark of STMicroelectronics ® 2001 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A. http://www.st.com